By Jim Perkins, Senior Principal Analogue FAE & MGTS at Texas Instruments and Dan Tooth, Principal Analogue Field Applications Engineer (MGTS)

Your new design needs to fit twice as much into half the space and cost nothing – sound familiar? You selected the smallest point-of-load regulator and generated the tightest layout you could with the most cost-effective passive components. So far so good. But then you look at the output ripple on your critical rails and it’s not what you expected. What’s going on?

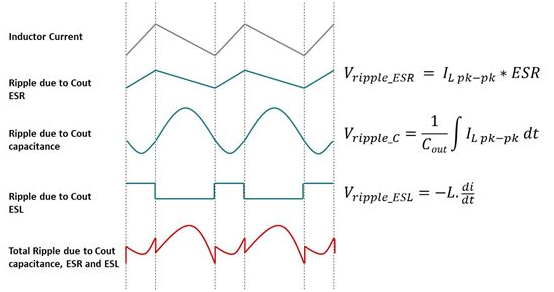

Let’s start by understanding what makes up the output ripple on a buck DC/DC regulator. It is a composite waveform. Traditionally only the three dominant elements shown in Figure 1 have been considered:

- A triangular wave generated by applying the inductor current ramp across the equivalent series resistance (ESR) of the output capacitors. A 22-µF X5R ceramic capacitor may have an ESR of only 2 mΩ. Considering an inductor peak-to-peak current ripple of 1 A, the ESR ripple is 2 mV (less if you’re using multiple parallel capacitors).

- A pseudo-sinusoidal component due to output capacitance. For the same output capacitor and ripple current as in the bullet point above, the capacitive ripple will be around 8 mV (less for multiple parallel output capacitors).

- A square component generated across the output capacitor equivalent series inductance (ESL). For a 22-µF X5R capacitor, the ESL is around 0.5 nH, which generates a ripple of about 2 mV.

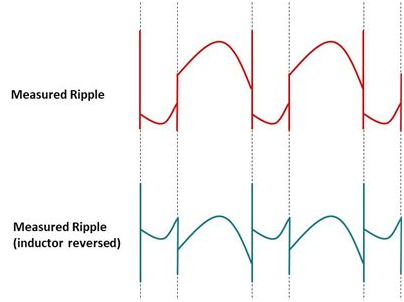

However, what you measure has spikes on the edges and a higher square-wave content that changes polarity when you reverse the inductor shown in Figure 2:

What has caused these undesirable components? And more importantly, what can you do about it?

Spikes

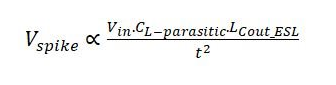

When you selected your inductor, the self-resonant frequency (SRF) was above your regulator switching frequency, so all was good. Let’s re-look at that – the inductor has an SRF because it has a parallel parasitic capacitance. Applying the fast edge of the switching voltage to the parasitic capacitance generates a large current spike through the capacitor, which in turn generates a large voltage spike across the ESL of the output capacitor (see Equation 1):

To reduce this spike:

- Select an inductor with a smaller parasitic capacitance. Look for the highest SRF value for the inductance and rating you need. Lower inductances tend to have lower parasitic capacitance (as do lower current ratings), so don’t over-specify the inductance or current rating.

- Reduce the output capacitance ESL. Choose the smallest capacitor package size that meets your output capacitance requirements. Using multiple smaller capacitors in parallel means the package size (and hence the ESL) of each capacitor can be smaller, while having inductors in parallel will also reduce the total ESL.

- Reduce the transient voltages (dV/dt) of the switch node (increase the value of t). Some regulators may allow direct control of the switch-node edge, but more often you may be able to place a small resistor in series with the bootstrap capacitor to slow the edge. This can impact efficiency, so the first two options are preferable.

Square wave

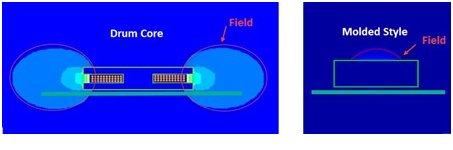

Let’s say that you selected a cost-effective, unshielded inductor. The magnetic field from an unshielded (or resin-shielded inductor) can spread beyond the physical body of the component. The simulation plots in Figure 3 show the field for an unshielded open drum inductor and a fully shielded molded inductor.

This compact layout has output capacitors sitting right next to the inductor. The escaping magnetic field couples to the ESL of the capacitors (and to a lesser extent the output track loops) and generates the square-wave component. When the inductor is reversed, the current in the inductor and the magnetic field is reversed (like swapping the dot in a coupled inductor), so the square-wave component is inverted.

To reduce this effect:

- Select a shielded inductor to reduce the leakage flux that generates this coupling. If you’re using unshielded or semi-shielded inductors, selecting an inductor that is larger in the x-y dimension but has a lower profile will reduce the airgap height and hence the fringing flux.

- Reduce the output capacitance ESL as described above.

- Don’t position the output capacitors and tracking directly next to the inductor, where the field is highest. Where space is critical, consider placing the inductor on the opposite side of the board to the rest of the regulator circuit in a clamshell construction. This moves the output capacitors away from the plane of the inductor where the magnetic field is strongest.

Now you can look at your output ripple waveform and unpack the different components. By choosing the right external passives and making some careful decisions on layout, you can still achieve a tiny, cost-effective solution and optimize the output ripple for your application.