The FPGA designs today are much more complex due to increased use of embedded processors, complex high speed IPs such as PCIe, DDR etc..Increased design complexity –demands high verification need and effort. Xilinx provides a rich set of tools such as Vivado® Design Suite or SDK to build and verify these complex systems.

The FPGA designs today are much more complex due to increased use of embedded processors, complex high speed IPs such as PCIe, DDR etc..Increased design complexity –demands high verification need and effort. Xilinx provides a rich set of tools such as Vivado® Design Suite or SDK to build and verify these complex systems.

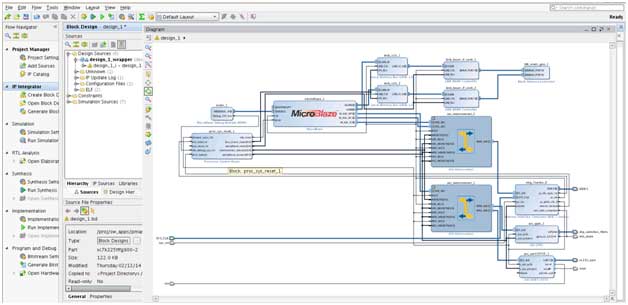

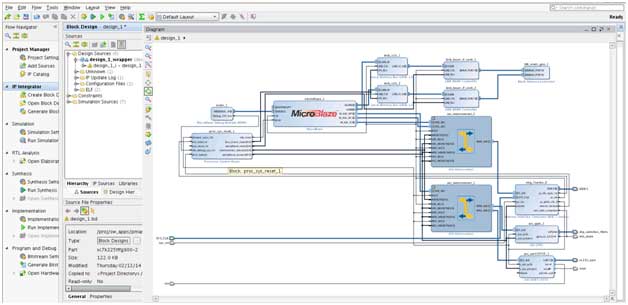

The Vivado IP integrator is an interactive design and verification environment, enabling you to build and verify a hierarchical system by graphically connecting IP provided by Xilinx, third parties, or the developer’s propriety IP, using interface level connections onto a design canvas with device, IP and board awareness. You can create designs interactively through the IP integrator design canvas GUI, or programmatically using a Tcl programming interface. Design teams can also use IPIto create asimulation environment with very low effort to verify their designs. Refer below links for more details on IP integrator:

http://www.xilinx.com/training/vivado/designing-with-vivado-ip-integrator.htm

Verification of embedded processor based applications on FPGA’s has become challenge for FPGA users on how to associate software application to the processor on FPGA.This tutorial shows the steps required to simulate designs with embedded processor based application using Vivado framework.

Step One: Creating systems/design with IPI:

Step One: Creating systems/design with IPI:

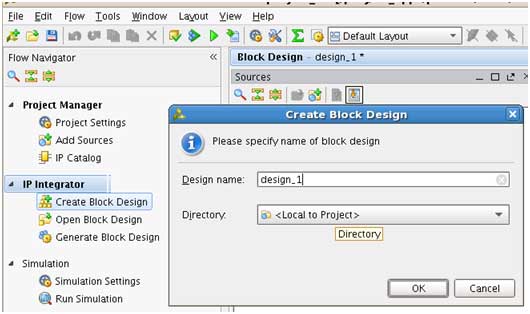

IPI based design can be created by clicking create block design under IP Integrator option available in flow navigator after creating project in Vivado.

- Use IPI-Block Design (refer to Figure 2) capability to create your design by customizing and hooking up various IPs

- Assign the address map for different peripherals using Address Editor tab.

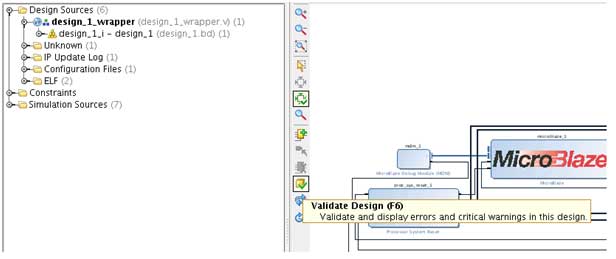

- After creating system, validate the BD (Block design), to make sure that all the connections are correct (refer to Figure 3)

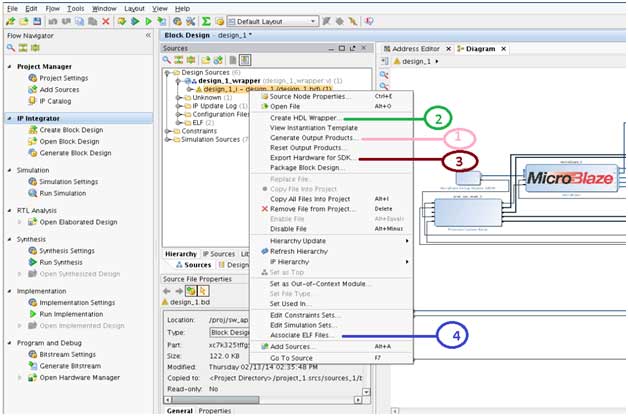

- Generate the output products of the BD design using the “Generate Output products” option (refer to figure 4 Option 1). At this stage Vivado generates all the necessary simulation files for Xilinx IPs and custom IPs

- Create HDL wrapper of the BD design using “Create HDL wrapper” option, which creates the toplevel wrapper of the design – isthe DUT in testbench (refer to 4 Option 2)

Step Two: Creating and associating Embedded SW application

- After creating the System in IPI, create the SW application by using “Export Hardware for SDK” option. This will launch the SDK with hardware platform details (refer to Figure 4 Option 3)

- Create new application project along with the BSP, build the project and make sure that the .elf (the software application to run on the embedded processor) is generated.

- Associate the .elf to Microblaze using “Associate elf file” option(refer to figure 4 Option 4). This will generate the corresponding memory files and it will initialize the memories with instructions incase Microblazeis executing from internal memories (LMBs). In case of external memories, user has to make sure that instructions are loaded/available in external memory models before the Microblaze comes out of reset. (http://www.xilinx.com/support/documentation/application_notes/xapp1180.pdf ).

Step Three: Creating test bench with simulation models

- Create test bench and use the HDL wrapper created by Vivado as DUT and instantiate in Test bench

- Instantiate all the simulation models of the peripherals outside of the FPGA, and memories which communicate with external world.

- For example for an external DDR memory, pull in the Micron memory model and configure that according to the memory setting in the system and instantiate it in the test bench.

- Similarly, for UART, write a UART model and instantiate it in test bench

- Connect all the models for external peripherals/components appropriately and feed the test inputs if required to the models

- You can have your own simulation code in test bench to define pass fail criteria and report status.

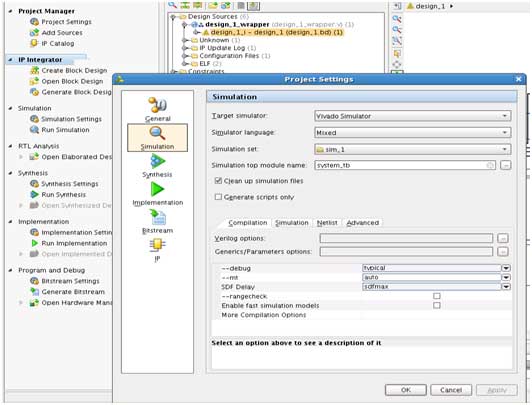

- Vivado supports QuestaSim,NCSim, VCS and its internal simulator as integrated simulators. If you are using one of these 2 simulators, set up the simulator and its relevant setting under simulation settings option available in flow navigator (refer to Figure 5)

- Launch the simulation using “Run Simulation”

- This will launch the corresponding simulator, and simulation will continue. To debug the design w.r.to embedded software, user can look at the instructions in the .elf file and can correlate with the contents on the Microblaze instruction bus.

Vivado IP Integrator allows you to verify/simulate the embedded software application. It provides easy interface to build the verification environment and reduces the verification effort.