February 24th -26th, 2015, Booth 578 in Hall 4

Eindhoven, December 2014 — JTAG Technologies BV (Eindhoven, The Netherlands), a vendor of test and debug tools based on boundary-scan, will showcase the following JTAGLive products in Hall 4, booth 578:

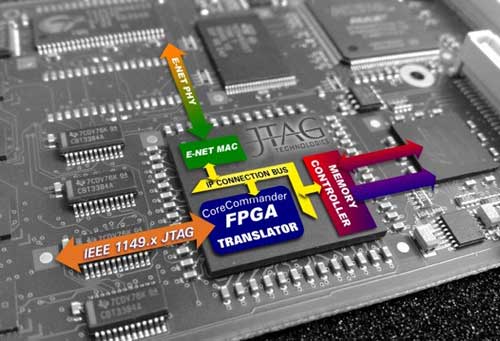

CoreCommander and JTAG Translator for FPGAs

Direct access to memory and peripheral controllers in FPGAs for testing, debugging and in-system programming

- Direct access to memory and peripheral (I/O) controllers in an FPGA through its JTAG interface

- Read data from, write data to memory and peripherals without software programming

- At-speed execution of read and write cycles

- Testing and debugging of the connections between an FPGA and memory and peripherals with at-speed bus cycles without software programming

- Easy programming of flash memory without software programming

JTAG Translator is an IP module from JTAG Technologies that provides a JTAG interface to the internal IP connection bus of an FPGA to which peripherals / peripheral controllers are connected. JTAG Translator is operated through a dedicated CoreCommander that can be used with JTAGLive and ProVision as well as with all our production packages. CoreCommander provides high-level functions to write data to and read data from memory and I/O addresses without software programming. CoreCommander functions are applied via the JTAG interface. The JTAG Translator IP module can be loaded in the FPGA for test configurations only, or it can be included as standard in functional designs.

JTAG Translator is an IP module from JTAG Technologies that provides a JTAG interface to the internal IP connection bus of an FPGA to which peripherals / peripheral controllers are connected. JTAG Translator is operated through a dedicated CoreCommander that can be used with JTAGLive and ProVision as well as with all our production packages. CoreCommander provides high-level functions to write data to and read data from memory and I/O addresses without software programming. CoreCommander functions are applied via the JTAG interface. The JTAG Translator IP module can be loaded in the FPGA for test configurations only, or it can be included as standard in functional designs.

With JTAG Translator the IP blocks which are already used in a design can be re-used for test or in-system programming purposes. Examples of existing IP blocks are interface controllers for SDR, DDR, Ethernet Mac, USB, UART, I2C, CAN, etc. These are readily available from different IP suppliers like Altera, Xilinx, OpenCores, etc.

Applications

CoreCommander is used in design debug, manufacturing test and (field) service for many different applications such as:

- Checking the connections between an FPGA and memory or I/O devices by writing data to and reading data back from these devices via the memory and peripheral controllers in the FPGA.

- Determining the right settings for the peripheral controller (DDR controller, flash memory controller, I/O controller) in combination with your particular memory or peripheral device. Write settings into the controller registers and verify whether proper access to memory or I/O is possible with those settings.

- Programming board (serial nr) specific data such as calibration values, a mac address or a timestamp in flash memory, or program an entire flash.

Support for new IEEE JTAG Standard (IEEE P1687) – New Demo – Revolutionary Extension to Basic IEEE 1149.1

Newly available as an addition to our standard range of tools, is a module aimed at the support of new IEEE P1687 (aka IJTAG – Internal JTAG) compliant devices that are currently under development. JTAG/P1687 has been devised as an evolutionary extension to the basic IEEE 1149.1 and IEEE 1500

Standards and describes how embedded (test) instruments within a device or S-O-C may be accessed using the conventional 4/5 wire JTAG port.

While the instruments themselves (typically HS-IO modules for high-speed interface testing like DDR3 etc.) are not described as part of the standard all the mechanisms for interacting with the instruments are. JTAG Technologies has therefore developed tools to read in the new P1687 description format and make available the features of all compliant devices to their customers.

The specific P1687 module supports the key language elements of the proposed standard, namely:- ICL- Instrument Connectivity Language that defines the hardware/logic interface to the instruments IP and; PDL – Procedural Description Language (a close relative of TCL) that defines the patterns or vectors that are applied and sensed via the logic interfaces in order to invoke the instruments’ IP functions. The P1687 tool contains all the necessary parsers and interpreters required to create working applications for P1687 compatible devices that are now emerging in some key industry sectors.

JTAGLive Studio – One package covers all needs

It is a comprehensive package of JTAG/boundary-scan tools that enable designers and manufacturing test engineers alike to develop complete test and programming applications – at an unprecedented [low] price level. The benefits offered by the JTAG Technology for debugging, testing and in-system programming are not limited to complex designs with many JTAG devices. Designs with only a few, even just one or two, JTAG devices can also greatly benefit from this technology during all stages of the life cycle. A toolset capable of handling even the most (very) complex boundary-scan designs, however, often is not economically feasible for a company that only uses a few JTAG devices in its designs. It establishes a new class of test and device-programming tool-set that dramatically lowers the cost of entry for test and hardware engineers, while still offering the many traditional benefits of JTAG/boundary-scan alongside newer technologies like processor-controlled test.

It works with or without design net-list data and can be used to test interconnects (from individual nets to an entire board), logic clusters, memories and more. Studio also includes device programming features that support JAM/STAPL and SVF data formats for CPLD and [FPGA] configuration PROM programming.

About JTAG Live

JTAG Live is the economic easy-to-use family of board debug tool from JTAG Technologies. The original offering for JTAG Live, first introduced in November 2009, comprised of three family members: Buzz, Clip and Script. Last year two new products were added to this family: BuzzPlus and AutoBuzz.