New Delhi, October 23, 2019 — Developers of spacecraft electronics use radiation-tolerant (RT) field programmable gate arrays (FPGAs) to create on-board systems that meet the demanding performance needs of future space missions, survive the brutal launch process and continue to operate reliably in the harsh environment of space. Extending its RT FPGA offering to bring

New Delhi, October 23, 2019 — Developers of spacecraft electronics use radiation-tolerant (RT) field programmable gate arrays (FPGAs) to create on-board systems that meet the demanding performance needs of future space missions, survive the brutal launch process and continue to operate reliably in the harsh environment of space. Extending its RT FPGA offering to bring

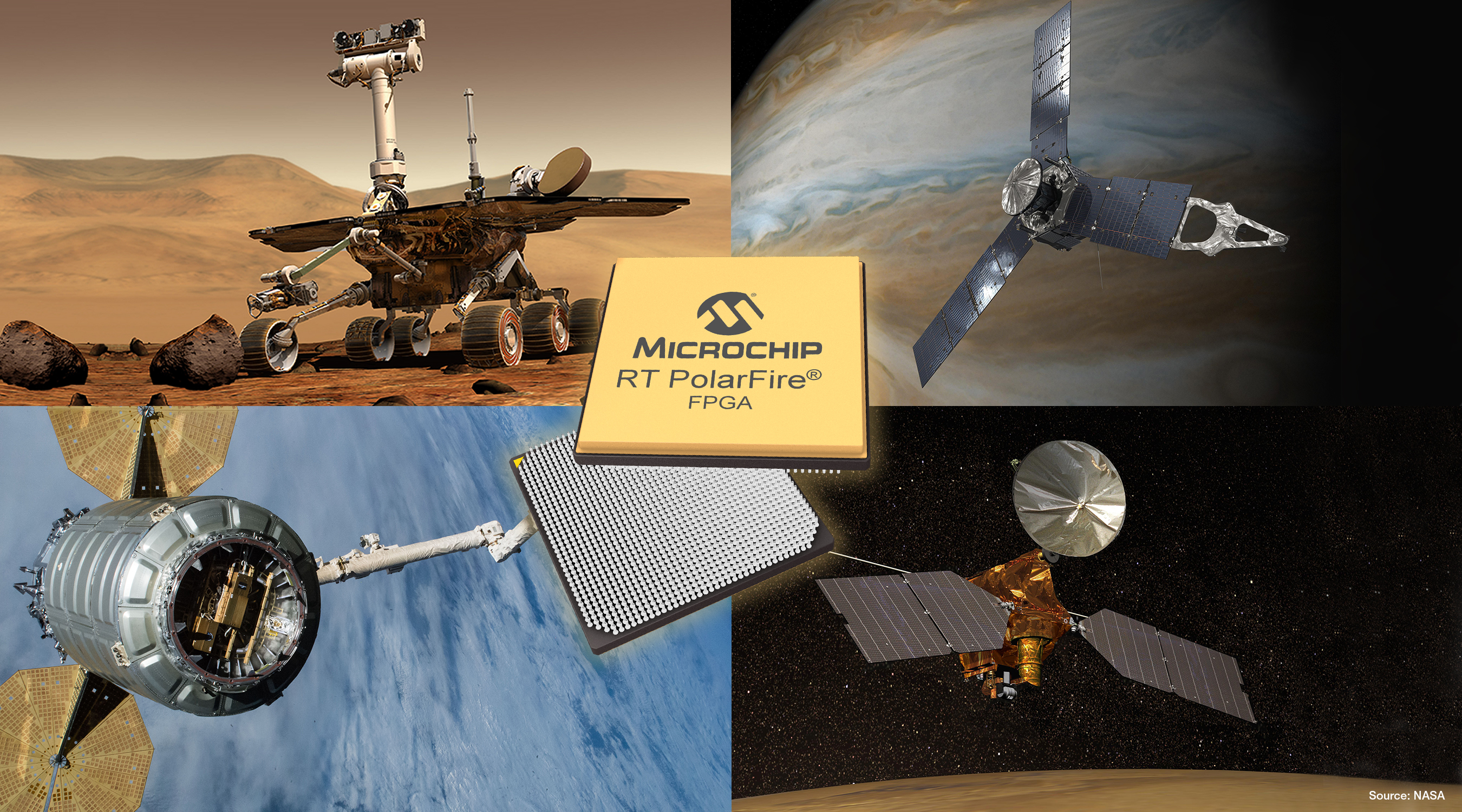

these capabilities to emerging high-performance space applications, Microchip Technology Inc. (Nasdaq: MCHP) today introduced the RT PolarFire FPGA that is optimized to meet the most demanding requirements in spacecraft payload systems’ high-speed data paths with the lowest possible power consumption and heat generation.

“We are supporting an evolving set of on-orbit space applications that need high levels of operating performance and density, low power consumption and minimal heat dissipation, while reducing system-level costs,” said Bruce Weyer, Vice President of Microchip’s FPGA business unit. “Our RT PolarFire FPGA enables the major leap in computing throughput required for these

applications including processing-intensive neural networks for object detection and recognition, high-resolution passive and active imaging, and high-precision remote scientific measurement, while maintaining a path to QML qualification.”

A growing number of space applications need greater computational performance so they can transmit processed information rather than raw data and make optimal use of limited downlink bandwidth. The RT PolarFire FPGA enables this at significantly lower cost and with faster design cycles than possible with application-specific integrated circuits (ASICs). It also significantly reduces power as compared to the alternative of using FPGAs based on static random access memory (SRAM) while eliminating their

vulnerability to radiation-induced configuration upsets. The RT PolarFire FPGA is supported by all necessary radiation data, specifications, package details and tools customers need to start new designs now, initially with the commercial version of the device.

The RT PolarFire FPGA builds on the success of Microchip’s RTG4 FPGA, which has been widely deployed in space applications that require its radiation-hardening by design against single event upsets (SEUs) and inherent immunity to single event latch-ups (SELs) and configuration upsets.

For space applications that require up to five times the computing throughput, the RT PolarFire FPGA provides 50 percent more performance and triple the logic elements and serializer-deserializer (SERDES) bandwidth. It also provides six times the amount of embedded SRAM to enable more system complexity than previously possible using FPGAs and withstands total ionizing dose (TID) exposure beyond the 100 kilorads (kRads) that is typical of most earth-orbiting satellites and many deep-space missions.

The RT PolarFire FPGA cuts power consumption to approximately half that of alternative SRAM-based FPGAs with equivalent density and performance. Its SONOS non-volatile (NV) technology enables its configuration switches to be implemented in a more power-efficient architecture that cuts development and bill of materials costs through simplified, less expensive and lighter power

system design while minimizing heat dissipation to reduce thermal management problems. Designs are further simplified as compared to using SRAM-based FPGAs because the RT PolarFire FPGA eliminates the cost, complexity and recovery downtime of mitigating configuration SEUs.

The RT PolarFire FPGA will undergo the standard process for meeting QML standards including class V qualification for highly critical applications. Microchip has lengthy experience achieving QML qualification for its RTG4 FPGAs and other products, which requires extensive and continuous testing including screening each wafer and package assembly lot.

Availability

Packaged in a hermetically sealed ceramic column grid array with integrated decoupling capacitors, Microchip’s RT PolarFire RTPF500T FPGA will be available and qualified for space-flight deployment in 2021. Customers can start designs now using the commercial PolarFire MPF500T FPGA with Microchip’s Libero® software tool suite that includes optional triple mode redundancy (TMR) synthesis support for implementing SEU mitigation where required, such as in control circuits. Development boards are available with the commercial PolarFire FPGA and will later include the RT PolarFire device in engineering model form. Available radiation data includes TID, SEL, configuration upsets, and upsets in unprotected D-flip flop (DFF) and memory.