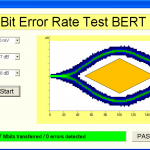

At the 2013 International Test Conference, GOEPEL electronic introduced an Automatic Application Program Generators (AAPG) for design validation and test of FPGA integrated high-speed I/O (HSIO) based on the ChipVORX® technology for FPGA Embedded Instruments. Users can now evaluate transmission channel quality by utilizing Bit Error Rate Tests (BERT). This provides a graphical evaluation per dynamic eye diagram to support design validation.

At the 2013 International Test Conference, GOEPEL electronic introduced an Automatic Application Program Generators (AAPG) for design validation and test of FPGA integrated high-speed I/O (HSIO) based on the ChipVORX® technology for FPGA Embedded Instruments. Users can now evaluate transmission channel quality by utilizing Bit Error Rate Tests (BERT). This provides a graphical evaluation per dynamic eye diagram to support design validation.

“The development towards FPGA based board designs is also accompanied by more and more high-speed I/O, difficult to test by traditional metrology due to continuously decreasing physical access. Our new solution addresses this very problem”, says Heiko Ehrenberg, Technology Officer for Embedded System Access for GOEPEL electronics in the USA. “Because of high automation level, the high-speed I/O’s FPGA parameters can be interactively defined, and become immediately effective without design synthesis, i.e. users can directly validate the influence on transfer quality. Furthermore, signals received in the silicon are recorded and visualized, which enables unaltered measurement results.”

About the Automatic Application Program Generator:

The new generator is another option in the integrated JTAG/Boundary Scan software platform SYSTEM CASCON™, enabling automatic generation of complete application scripts for FPGA embedded HSIO test instruments. These are chip-dependent instrument selections, establishment within an FPGA, addressing, configuration, procedural control, qualification of generated data and graphical eye visualization.

The AAPG connects ChipVORX model integrated instrument information with the intrasystem data base for structural and functional UUT (unit under test) description and protocol-specific user guidelines for configuration of the target FPGA’s high-speed I/O channels. The fully automatically generated script is based on the SYSTEM CADCON™ integrated standard language CASLAN (CAScon LANguage) and can be executed on each run-time station without additional options. Gang applications are also supported.

About Bit Error Rate Test (BERT):

So called Bit Error Rates (BER) are measured to evaluate the channel quality in digital transmission systems. BER is the relation between faulty transported bits and the total number of transported bits in a certain time interval. The equipment consists basically of the pattern generator, a transceiver with error detector and a clock generator, synchronising both. The bit patterns, created by the pattern generator, are in particular important for the quality of the Bit Error Rate Test, as they have critical influence on the fault stimulation during the transmission (stress pattern).

About Chip Embedded Instruments:

Chip embedded Instruments are permanently integrated or temporarily implemented test and measurement functions (T&M) in an integrated circuit. Virtually, they are the counterpart to external T&M instruments as they don’t require invasive contacting by means of probes or nails. Hence, the problem of signal distortion in high-speed designs by parasitic contacting effects is omitted. Chip embedded Instruments are part of the so called Embedded System Access (ESA) technologies that are currently the most modern strategy for validation, test and debug as well as programming of complex boards and systems. They can be utilised throughout the entire product life cycle, enabling improved test coverage at reduced costs.

About ChipVORX®:

ChipVORX is an IP-based technology for implementation, access and control of Chip embedded Instruments via IEEE Std. 1149.x/JTAG. It also supports FPGA embedded instruments in the form of softcores. The ChipVORX library currently contains more than 300 different test and measurement instruments for all leading FPGA platforms. Some of these instruments are frequency meters and high-speed Flash programmers as well as IP for at-speed access test of dynamic RAM devices.

About the development, funding and availability:

The BERT instruments development as prototypes and their integration into respective system software is the result of a strategic cooperation between GOEPEL electronic and Testonica Lab. The ChipVORX® IP models for BERT will be supported in SYSTEM CASCON™ starting from version 4.6.3 , and are activated per license manager just like the system software. SYSTEM CASCON™ is GOEPEL electronic’s professional JTAG/Boundary Scan development environment with currently more than 45 fully integrated ISP, test and debug tools. In terms of hardware, ChipVORX is completely supported in the platform SCANFLEX®.

The project upon which this publication is based was funded by the Federal Minister of Education and Research within the frame of the Eurostars funding programme (E! 5568 COMBOARD).