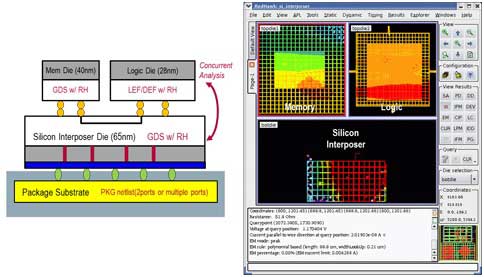

RedHawk is the industry-standard dynamic power integrity solution from ANSYS with the capacity to handle designs with over billion gates, while maintaining sign-off accuracy. It analyses the effects of simultaneous switching noise (core, memory, I/O), decoupling capacitance (intentional and intrinsic), on-chip and off-chip (package) inductance. RedHawk enables power methodologies from RTL to Gates, across Chip, Package and System, and supports the emerging 3D-IC / multi-die initiatives.

Benefits and Applications

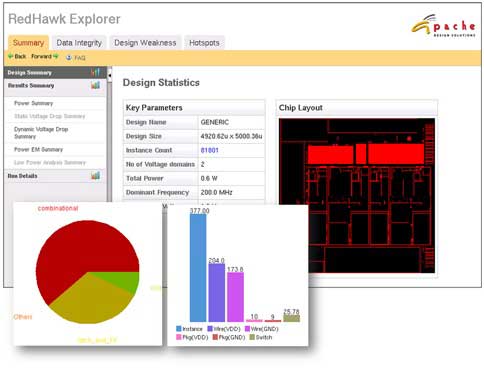

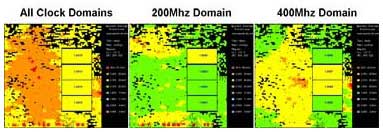

RedHawk allows designers to explore and identify physical design weaknesses (RHE), automatically repair supply noise source (FAO), analyse the impact of dynamic voltage drop on timing and jitter (PSI), verify power and signal EM (SEM), validate ESD protection robustness (PathFinder™), provide a power delivery network model profile for system-level analysis (CPM™), and allow modeling, simulation and debug of 3D-IC designs (MDO).

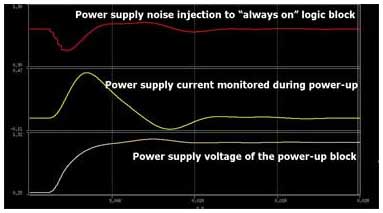

RedHawk (ALP) performs rush-current and ramp-up analysis, multi-mode verification, and intelligent switch optimization for ultra-low-power design techniques including multiple voltage islands, MTCMOS (power-gating), VTCMOS (substrate back-biasing), switched memories, and on-chip LDO (low drop-out) voltage regulators.

RedHawk enables designers to meet the power budget, power delivery integrity, and power-induced noise immunity targets for their IC.